What are IP Addresses? IP addresses are fundamental to the digital infrastructure of any business…

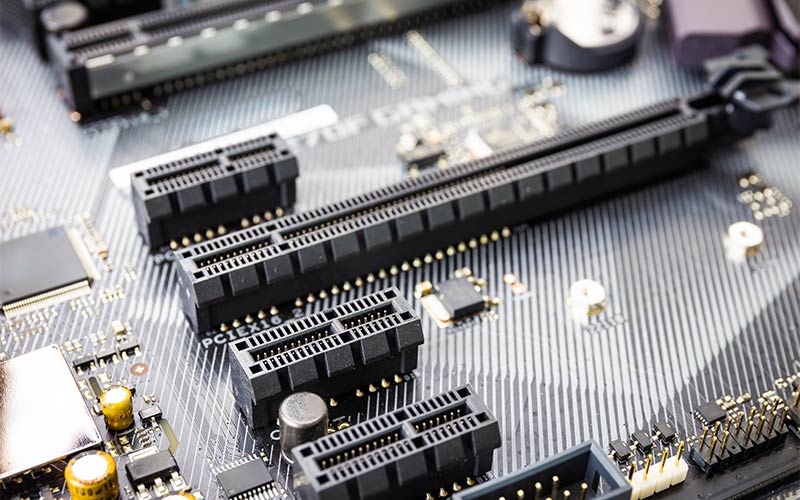

Computer Expansion Bus

A computer expansion bus is a computer interface that allows additional hardware components to be connected to a computer system. It is a type of communication interface that provides a standardized way for different hardware components to communicate with each other and with the computer’s central processing unit (CPU). The expansion bus provides a way for hardware components to access the computer’s memory, I/O ports, and other system resources.

There are several types of expansion buses, and each type of expansion bus has different specifications for data transfer rate, number of devices that can be connected, and other features. The most commonly used expansion bus today is Peripheral Component Interconnect Express (PCIe or PCI-e), which will be the focus of this blog post. PCIe provides high-speed data transfer and support for multiple devices, making it an ideal interface for connecting a wide range of hardware components.

Since its inception in 2003, PCIe 1.0 has undergone several advancements. The evolution of the standard has been driven by the Peripheral Component Interconnect Special Interest Group (PCI-SIG), an industry consortium that develops and manages PCIe technology. In this blog post we will take a closer look at the evolution of the PCIe standard, beginning with PCIe 1.0 through PCIe 5.0, and looking forward to what can be expected in the future with both PICe 6.0 and PCIe 7.0.

How does a PCIe Interface Transfer Data?

PCIe transfers data using a point-to-point serial communication protocol, which is a type of communication protocol that enables data to be transmitted between two devices over a single communication channel. The data transfer mechanism involves the use of lane slots, which are an important component of the PCIe interface.

A lane slot is a full-duplex communication channel that enables data transfer in both directions, simultaneously. The number of lane slots available on a PCIe interface determines its bandwidth capacity, with each lane slot being made up of two pairs of wires (one for transmitting data and one for receiving data).

When a device is connected to the motherboard through a PCIe interface, the number of lane slots it uses determines the available bandwidth. For example, a device that uses x8 lane slots would have twice the bandwidth of a device that uses x4 lane slots. This allows devices to transfer large amounts of data quickly and efficiently, making PCIe ideal for high-performance hardware components such as graphics cards, solid-state drives (SSDs), and network adapters.

In addition to lane slots, PCIe uses serial transmission (transmitting data one bit at a time over a single communication channel), data packetization, and advanced error correction mechanisms to ensure fast and reliable data transfer. Data is transmitted in packets over the PCIe interface, with each packet containing the data being transferred, as well as addressing and control information that helps the devices communicate with each other. The advanced error correction ensures that data is transmitted accurately and without errors.

PCIe Standards Over Time

- PCIe 1.0 was the first version of the standard, released in 2003. It provided a significant improvement over the previous generation of PCI (Parallel Computing Interface) with a faster transfer rate of 2.5 Gbps (gigabits per second) per lane and full-duplex communication. The standard was commonly found in consumer desktop and laptop computers, as well as some entry-level servers.

- PCIe 2.0 was released in 2007 and doubled the transfer rate of PCIe 1.0 to 5 Gbps per lane, allowing for improved data transfer speeds between components. It was commonly found in high-performance desktops, workstations, and servers.

- PCIe 3.0 was released in 2010 and brought a further increase in transfer rate to 8 Gbps per lane. It was widely adopted in high-end desktops, workstations, and servers, as well as in some high-performance gaming laptops.

- PCIe 4.0 was released in 2017 and increased the transfer rate to 16 Gbps per lane. It was first adopted in high-performance desktops, workstations, and servers, and has since been adopted in some high-end gaming laptops.

- PCIe 5.0 was released in 2019 and increased the transfer rate to 32 Gbps per lane. It has been adopted in high-performance desktops, workstations, and servers, and is being used in some high-performance gaming laptops and gaming desktops.

Looking Forward

- PCIe 6.0 is currently under development and is expected to be released in the near future. The standard is expected to bring a significant increase in transfer rate, with a target of 64 Gbps per lane. It will be used in high-performance desktops, workstations, and servers, as well as in some cutting-edge cloud computing and machine learning applications.

- PCIe 7.0 is also under development and is expected to be released after PCIe 6.0. It should bring a further increase in transfer rate, with a target of 128 Gbps per lane. PCIe 7.0 will be used in cutting-edge cloud computing and machine learning applications, in some high-performance desktops, workstations, servers, and likely even newer technologies that have not yet been developed.

Table showing the comparison of gigabits per second (Gbps) of bandwidth for different versions of PCIe with varying slot sizes:

| Slot Size | PCIe 1.0 | PCIe 2.0 | PCIe 3.0 | PCIe 4.0 | PCIe 5.0 | PCIe 6.0 | PCIe 7.0 |

| x1 | 2.5 | 5 | 8 | 16 | 32 | 64 | 128 |

| x4 | 10 | 20 | 32 | 64 | 128 | 256 | 512 |

| x8 | 20 | 40 | 64 | 128 | 256 | 512 | 1024 |

| x16 | 40 | 80 | 128 | 256 | 512 | 1024 | 2048 |

The evolution of PCIe standards has brought significant improvements in performance and functionality over the years. Each new version of the standard brings increased performance and capabilities, making it possible for developers to create even more powerful and innovative applications. It is a safe bet to expect a continuing trend in that direction as innovation of new applications and technologies drive the demand for a never-ending improvement to performance.